Logique séquentielle/Implantation en D et JK

Limitation en fréquence

[modifier | modifier le wikicode]Les conditions d'état associées à l'horloge dans une commande synchrone doivent être stables soit pendant toute la durée de l'horloge soit pendant une plage de temps tsetup et thold autour du front actif de l'horloge. Soyons un peu plus précis en définissant un certain nombre de paramètres temporels qui doivent être respectés pour un fonctionnement synchrone correct.

- Tsetup représente le temps pendant lequel l'entrée doit être stable avant le front d'horloge pour être prise en compte correctement.

- Thold représente la même chose mais après le front d'horloge.

- tCKO : lorsqu'un front d'horloge arrive les sorties ne seront vraiment mises à jour qu'un temps tCKO après.

Chaque composant possède une documentation sur ces temps.

Pour examiner les conséquences de ces paramètres temporels, nous présentons ci-dessous deux versions d’un même compteur :

Exercice 1

[modifier | modifier le wikicode]Pour un temps moyen tp de 20 ns par porte et tCKO=tp par bascule, quelle serait la fréquence maximum applicable en entrée pour un fonctionnement correct pour les deux schémas ci-dessus. Même question en tenant compte du "set-up time" : Tsetup = 30 ns

Exercice 2

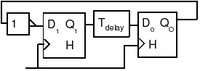

[modifier | modifier le wikicode]Déterminer la période d'horloge minimum pour un bon fonctionnement de ce circuit :

(Paramètres : Tsetup = 5 ns min, Thold 3 ns, 2,5 < tCKO < 12 ns, Tdelay = 10 ns temps de propagation de l'inverseur 6 < tp < 9 ns.) tCKO : clock to output

Les raisonnements liés aux paramètres temporels sont compliqués par le fait que certains temps sont en série et d'autres sont en parallèle. N'oubliez pas que le montage est synchrone ! Pour commencer partez d’un front d'horloge et demandez-vous quand, au minimum, vous pourrez envoyer le front d'horloge suivant.

Initialisation

[modifier | modifier le wikicode]Lors de la mise sous tension les bascules en circuits intégrés sont initialisées à 0 (les circuits programmables à 1). Pour être sûr de l'initialisation il faut utiliser les entrées asynchrones ou réaliser une initialisation synchrone :

Forçage asynchrone

[modifier | modifier le wikicode]Ce type de montage se rencontre en pratique même s'il est déconseillé à utiliser.

Un compteur asynchrone : le 7490 (TTL)

[modifier | modifier le wikicode]Ce circuit est composé d’un diviseur par 2 et d’un diviseur par 5. Par mise en cascade, il permet une division par 10. Le cycle à 10 positions est obtenu par la mise en cascade (QA relié à Horloge B). Le cycle ayant un rapport cyclique 0.5 est appelé Bi-quinaire et l'autre comptage BCD. Il comprend d’autre part une entrée de forçage à 0 et une entrée de forçage à 9.

Exercice 3 (7490)

[modifier | modifier le wikicode]En connectant la sortie A à l'entrée "Horloge B" examiner la séquence des états. Même travail en connectant la sortie D à l'entrée "Horloge A". Lequel représente le comptage BCD ?

Exercice 4

[modifier | modifier le wikicode]Réaliser un générateur de signaux triphasés (120°). Le rapport cyclique sera 0,5. Montrer qu’il faut nécessairement 6 états pour le réaliser. Que faire des 2 états restants ? Écrire le programme VHDL correspondant.

Exercice 5

[modifier | modifier le wikicode]En utilisant trois bascules D et de la logique combinatoire, réaliser un circuit qui réalise les états suivants. Q2Q1Q0 = 0,1,3,2,6,7,5,4,0… Dessiner le diagramme d'évolution et trouver les équations de récurrence.