Bascules électroniques/RS

On désigne par bascule une microstructure séquentielle qui, pour une combinaison d'états d'entrée, présente sur ses sorties 2 états stables complémentaires l'un de l'autre.

Prérequis

[modifier | modifier le wikicode]État antérieur

[modifier | modifier le wikicode]Étant donné que l’on travaille en logique séquentielle (c'est-à-dire que l'état de la sortie est le résultat d’une séquence, c'est-à-dire de combinaisons temporellement successives des entrées), à un certain moment, il faut connaitre l'état précédant un évènement.

Pour cela nous utiliserons la notation suivante :

- est l'état de la sortie logique Q à l'instant n. Par convention, l'instant n est l'instant actuel.

- était donc l'état de la sortie logique Q à l'instant n-1, c'est-à-dire à l'instant précédant l'évènement faisant évoluer la bascule.

- sera donc l'état de la sortie logique Q à l'instant n+1, c'est-à-dire à l'instant suivant l'évènement et faisant donc évoluer la bascule.

À 2 portes NAND

[modifier | modifier le wikicode]

À la mise sous tension de la bascule, les sorties peuvent prendre l'une des deux combinaisons possibles complémentaires :

- Q = 0 et = 1

- Q = 1 et = 0

Il en résulte le fonctionnement suivant :

- Un niveau logique bas sur l'entrée S si l'entrée R est au niveau logique haut provoque la mise à 1 de Q et la mise à 0 de

- Un niveau logique bas sur l'entrée R si l'entrée S est au niveau logique haut provoque la mise à 0 de Q et la mise à 1 de

- Lorsque R et S sont à un niveau logique haut, Q et ne changent pas d'état

- Lorsque R et S sont à un état logique bas, Q et sont dans un état non logique. Cette situation est donc à proscrire

Table de vérité

[modifier | modifier le wikicode]

Cette bascule, simple, a quelques inconvénients :

- Les entrées fonctionnent l'une sur un front descendant alors que l'autre entrée doit être à un état haut. Il serait plutôt logique que les entrées soient naturellement de niveau bas et qu'ensuite ce soit un front montant qui fasse évoluer la bascule.

Ceci peut être facilement fait en rajoutant 2 portes inverseuses en entrée, ou alors en remplaçant les 2 portes NAND par 2 portes NOR

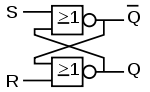

À 2 portes NOR

[modifier | modifier le wikicode]

À la mise sous tension de la bascule, les sorties peuvent prendre l'une des deux combinaisons possibles complémentaires :

- Q = 0 et = 1

- Q = 1 et = 0

Il en résulte le fonctionnement suivant :

- Un niveau logique haut sur l'entrée S si l'entrée R est au niveau logique bas provoque la mise à 1 de Q et la mise à 0 de

- Un niveau logique haut sur l'entrée R si l'entrée S est au niveau logique bas provoque la mise à 0 de Q et la mise à 1 de

- Lorsque R et S sont à un niveau logique bas, Q et ne changent pas d'état

- Lorsque R et S sont à un niveau logique haut, Q et sont dans un état non logique. Cette situation est donc à proscrire.

Table de vérité

[modifier | modifier le wikicode]

Conclusion 1

[modifier | modifier le wikicode]On se retrouve ainsi avec cette microstructure, appelée Bascule RS, et dont la représentation est la suivante :

L'entrée S est celle qui met à 1 la sortie Q, elle porte ainsi le nom de Set, et inversement l'entrée R mettant à 0 la sortie Q porte le nom de Reset.

Mais cette porte a un inconvénient majeur, à savoir qu'elle peut enregistrer un signal parasite sur l'entrée R ou S, faisant évoluer la bascule alors qu’il n'y avait pas lieu d'être.

Pour éviter ce problème, il suffit de valider la bascule pendant un temps très court durant lequel la bascule va observer l'état de ses entrées, et ensuite évoluera en fonction de celles-ci, c’est la bascule RSH

Bascule RSH

[modifier | modifier le wikicode]Fonctionnement asynchrone et synchrone

[modifier | modifier le wikicode]- Fonctionnement asynchrone

En fonctionnement asynchrone, les changements d'état des fonctions s'effectuent au fur et à mesure de la propagation des signaux le long d’une chaine de bascules.

- Fonctionnement synchrone

En fonctionnement synchrone, les changements d'état des fonctions sont commandés à des instants déterminés par une base de temps (appelée Horloge ou Clock), très souvent commune à plusieurs parties d’un circuit.

Tables de vérité

[modifier | modifier le wikicode]

Conclusion 2

[modifier | modifier le wikicode]

L'inconvénient de la bascule RS est réduit par la présence et la prise en compte des informations R et S sur un état logique de C, sans toutefois être éliminé. En effet, tant que C valide les entrées R et S, la bascule peut toujours enregistrer un parasite. Il faut donc réduire la validité par C à son strict minimum, c'est-à-dire non plus sur un état logique, mais sur un changement de valeur du signal, c'est-à-dire un front. On construit ainsi une bascule qui n'est plus une bascule RS, mais une bascule JK.